# **CSE7759B User Manual**

# Calibration-free Electric Energy Measuring Chip

Rev.1.2

芯海科技(深圳)股份有限公司 地址:深圳市南山区蛇口南海大道1079号花园城数码大厦A座9楼 电话:+(86755)86169257 传真:+(86755)86169057 网站:www.chipsea.com 邮编:518067 微信号:芯海科技

## **Revision History**

| <b>Revision Number</b> | History                                                                                                                                            | Time               |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Rev.1.0                | Initially issued                                                                                                                                   | September 11, 2017 |

| Rev.1.1                | <ol> <li>table 3-4,Added adj.3</li> <li>Added 3.5 chip reset</li> </ol>                                                                            | November 13, 2017  |

| Rev.1.2                | <ol> <li>Change the 3.6.2 voltage and power formula</li> <li>Change 3.7.2 F'<sub>CF</sub> formula</li> <li>Change the voltage and power</li> </ol> | December 25, 2017  |

|                        | formula in the 3.8.1 and 3.8.3 flow charts                                                                                                         |                    |

本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。 This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format without prior permission of CHIPSEA

| REVISI | DN HISTORY2                                                                                      |

|--------|--------------------------------------------------------------------------------------------------|

| 1 F    | JNCTIONAL DESCRIPTION OF THE CHIP4                                                               |

| 1.1    | Main Characteristic Function of the Chip                                                         |

| 1.2    | PIN DESCRIPTION OF THE CHIP                                                                      |

| 2 C    | HARACTERISTIC DESCRIPTION OF THE CHIP                                                            |

| 2.1    | Absolute Maximum Ratings                                                                         |

| 2.2    | RECOMMENDED OPERATING CONDITIONS                                                                 |

| 2.3    | ANALOG CHARACTERISTICS                                                                           |

| 2.4    | DIGITAL CHARACTERISTICS                                                                          |

| 2.5    | Switching Characteristics                                                                        |

| 3 A    | PPLICATION OF THE CHIP                                                                           |

| 3.1    | TYPICAL APPLICATION OF CSE7759B                                                                  |

| 3.2    | SIGNAL FREQUENCY OF ACTIVE POWER FCF                                                             |

| 3.3    | Measuring Range                                                                                  |

| 3.4    | SERIAL PORT PROTOCOL                                                                             |

| 3.5    | Chip Reset                                                                                       |

| 3.6    | CALIBRATION MODE                                                                                 |

| 3.     | 6.1 Calibration Address Selection                                                                |

| 3.     | 6.2 Delivery Calibration Parameters as Well as Current, Voltage and Power Formula of the Chip 20 |

| 3.7    | ELECTRIC QUANTITY CALCULATION                                                                    |

| 3.     | 7.1 Frequency of CF                                                                              |

| 3.     | 7.2 Current Example of Electric Quantity Calculation                                             |

| 3.8    | VOLTAGE, CURRENT, ACTIVE POWER CALCULATION REFERENCE FLOW CHART                                  |

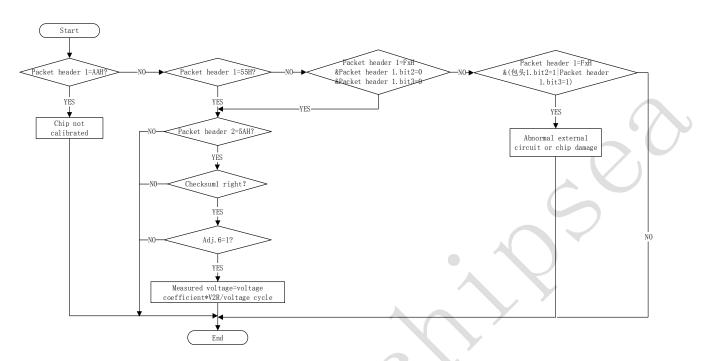

| 3.     | 8. 1 voltage operation reference flow chart                                                      |

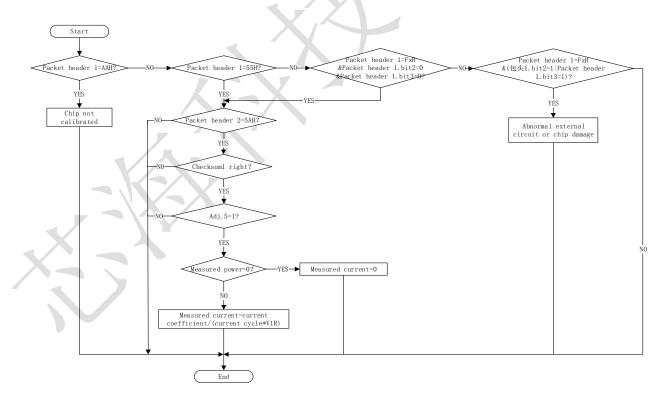

| 3.     | 8.2 current operation reference flow chart                                                       |

| 3.     | 8.3 Active power operation reference flow chart                                                  |

| 3.9    | BOOT THRESHOLD AND SHUNT RUNNING PREVENTION OF THE CHIP                                          |

| 3.10   |                                                                                                  |

| 3.1    | BUILT-IN REFERENCE SOURCE                                                                        |

| 4 P.   | ACKAGING OF CSE7759B                                                                             |

3/25

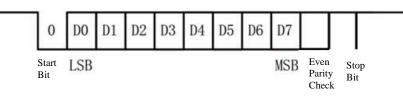

## **1** Functional Description of the Chip

CSE7759B is a single-phase multi-function measuring chip, provides high-frequency pulse CF for measuring electric quantity and may read relevant parameters of current, voltage and power (such as coefficient, cycle) directly through UART; baud rate of serial port is 4800bps  $(\pm 2\%)$  8-bit data with 1 even parity check and 1 stop bit. This chip is packaged in SOP8.

#### 1.1 Main Characteristic Function of the Chip

- 1. The cumulative error of the charge is  $\pm 2\%$ .

- 2. For current RMS, voltage RMS and power error range, see section 2.3

- 3. Baud rate of UART communication protocol of serial port is 4800bps.

- 4. Built-in power supply monitoring circuit; the chip will be enter reset state when power supply voltage is lower to 4V.

- 5. Built-in 2.43V voltage reference source.

- 6. 5V single power supply; operating current is smaller than 5mA.

- 7. Main application area: Occasions needing to meter voltage, current and power, such as single-phase multifunction watt-hour meter, measuring socket and data display instrument etc.

RI

CF

ΤI

VSS

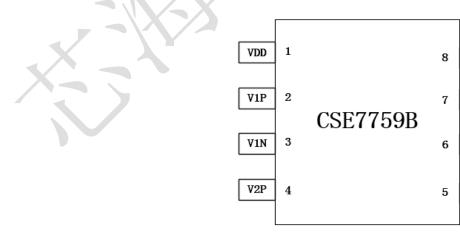

#### 1.2 Pin Description of the Chip

CSE7759B is packaged in SOP8.

4/25

## Figure 1: Chip Pin Diagram

## Table 1.1 CSE7759B Pin Description

| Pin | Pin  | Input/ Output           | Description                                        |          |  |  |  |  |

|-----|------|-------------------------|----------------------------------------------------|----------|--|--|--|--|

| No. | Name |                         |                                                    | $\wedge$ |  |  |  |  |

| 1   | VDD  | Chip- power             | Chip- power supply                                 |          |  |  |  |  |

|     |      | supply                  |                                                    |          |  |  |  |  |

| 2,3 | V1P, | Ι                       | Current differencing signal input terminal.        |          |  |  |  |  |

|     | V1N  |                         | Maximum differencing input signal is ±43.75mV      |          |  |  |  |  |

|     |      |                         | When the current signal is not used, the VIP and   |          |  |  |  |  |

|     |      |                         | V1N shall be short received VSS                    |          |  |  |  |  |

| 4   | V2P  | Ι                       | Voltage signal positive input terminal. Maximum    |          |  |  |  |  |

|     |      |                         | input signal is±700mV                              |          |  |  |  |  |

|     |      |                         | When the voltage signal is not used, the V2P shall |          |  |  |  |  |

|     |      |                         | be short connected to VSS                          |          |  |  |  |  |

| 5   | VSS  | Chip- ground            | Chip- ground                                       |          |  |  |  |  |

| 6   | TI   | 0                       | UART transmit port                                 |          |  |  |  |  |

| 7   | CF   | 0                       | Output active high-frequency pulse; duty ratio of  |          |  |  |  |  |

|     |      | $\langle \cdot \rangle$ | 50%                                                |          |  |  |  |  |

| 8   | RI   | Ι                       | UART receive port; reserved.                       |          |  |  |  |  |

本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。 This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format without prior permission of CHIPSEA

#### 2 **Characteristic Description of the Chip**

#### 2.1 Absolute Maximum Ratings

| Parameters                    | Symbol            | Min.  | Typica  | Max.    | Unit |  |

|-------------------------------|-------------------|-------|---------|---------|------|--|

|                               |                   | Value | l Value | Value   | 0    |  |

| power supply                  | VDD               | -0.3  | -       | +6.0    | V    |  |

| V1P, V1N, V2P                 |                   | -2    |         | +2      | V    |  |

| Analog input voltage          | V <sub>INA</sub>  | -0.3  | -       | VDD+0.3 | V    |  |

| Digital input voltage         | V <sub>IND</sub>  | -0.3  | -       | VDD+0.3 | V    |  |

| Digital output voltage        | V <sub>OUTD</sub> | -0.3  |         | VDD+0.3 | V    |  |

| Operating ambient temperature | T <sub>A</sub>    | -40   | -       | 85      | C    |  |

| Storage temperature           | T <sub>stg</sub>  | -65   | -       | 150     | °C   |  |

# 2.2 Recommended Operating Conditions

| Parameters        | Symbol         | Min.<br>Value | Typical<br>Value | Max.<br>Value | Unit |

|-------------------|----------------|---------------|------------------|---------------|------|

| power range       | VDD            | 4.5           | 5.0              | 5.5           | V    |

| Temperature range | T <sub>A</sub> | -40           | -                | 85            | °C   |

## 2.3 Analog Characteristics

VDD = 5V, GND = 0V,  $25^{\circ}$ C (unless otherwise stated)

| Parameters                                               | Symbo<br>l | Min.<br>Value | Typical<br>Value | Max.<br>Value | Unit |

|----------------------------------------------------------|------------|---------------|------------------|---------------|------|

| Analog input (all channels)                              | I          |               |                  | I             |      |

| Common-mode signal                                       |            | -1            | -                | 1             | V    |

| Analog input                                             |            |               |                  |               |      |

| Crosstalk to voltage channel in full<br>range (50, 60Hz) |            | -             | -100             | -             | dB   |

| Input capacitance                                                 | IC                 | -   | 6.4      | -       | pF             |   |

|-------------------------------------------------------------------|--------------------|-----|----------|---------|----------------|---|

| Equivalent input impedance:<br>Current channel<br>Voltage channel | EII                |     | 500<br>6 | -       | kΩ<br>MΩ       |   |

| Equivalent input noise:<br>Current channel<br>Voltage channel     | NI                 | -   | -        | 2<br>20 | μVrms<br>μVrms | 0 |

| Power supply                                                      |                    |     |          | C       |                |   |

| Current consumption<br>(VDD = 5 V)                                | Ι                  |     | 4        |         | mA<br>mA       |   |

| Power consumption<br>(VDD = 5 V)                                  | PC                 | -   | 20       |         | mW             |   |

| Low voltage threshold for power failure detection                 | PMLO               |     | 4        | -       | V              |   |

| High voltage threshold for power failure detection                | РМНІ               |     | 4.3      | -       | V              |   |

| Built-in reference voltage                                        |                    |     |          |         |                |   |

| Reference voltage                                                 | VREF               | 2.3 | 2.43     | 2.55    | V              |   |

| Temperature excursion                                             | TC <sub>VREF</sub> | -   | 25       | -       | ppm/°C         |   |

## Measurement accuracy (measuring relative error and absolute error of the parameter)

| Parameters                                                                     | Symbol | Min.  | Typical | Max.  | Unit |  |  |  |  |

|--------------------------------------------------------------------------------|--------|-------|---------|-------|------|--|--|--|--|

|                                                                                |        | Value | Value   | Value |      |  |  |  |  |

| Current: 1mR sampling resistance (ideal value, without resistance error), full |        |       |         |       |      |  |  |  |  |

| range of the current is 30.9A                                                  |        |       |         |       |      |  |  |  |  |

| 30.9A~250mA (relative error)                                                   |        | -2    | 1       | 2     | %    |  |  |  |  |

| 249mA~60mA (absolute error)                                                    |        |       | 10      | 15    | mA   |  |  |  |  |

| Min. measured value of current (to                                             |        |       | 60      |       | mA   |  |  |  |  |

| be determined by overall noise)                                                |        |       |         |       |      |  |  |  |  |

| No-load current (to be determined by                                       |            |         | 60           |        | mA  |   |  |

|----------------------------------------------------------------------------|------------|---------|--------------|--------|-----|---|--|

| overall noise)                                                             |            |         |              |        |     |   |  |

| Voltage: 1MR divider resistance (ide                                       | eal value, | without | resistance e | error) | I   |   |  |

| Voltage measurement range:                                                 |            | -2      | 1            | 2      | %   |   |  |

| 80V~260V(relative error)                                                   |            |         |              |        |     |   |  |

| Power: (ideal value, without current sampling resistance error and divider |            |         |              |        |     |   |  |

| resistance error)                                                          |            |         |              |        | . C | ) |  |

| Above 55W (relative error)                                                 |            | -2      | 1            | 2      | %   |   |  |

| Below 55W (absolute error)                                                 |            |         | 1            | 2.5    | W   |   |  |

| Min. measured value of power (to be                                        |            |         | 3            |        | W   |   |  |

| determined by overall noise)                                               |            |         |              |        |     |   |  |

| No-load power (to be determined by                                         |            |         | 0            |        | W   |   |  |

| overall noise)                                                             |            |         | Y            |        |     |   |  |

## 2. 4 Digital Characteristics

VDD = 5V, GND = 0V,  $25^{\circ}$ C (unless otherwise stated)

| Parameters                        | Symbol          | Min.    | Typical   | Max.  | Unit |  |  |  |

|-----------------------------------|-----------------|---------|-----------|-------|------|--|--|--|

| T al ancters                      | Symbol          | Value   | Value     | Value | Unit |  |  |  |

| Master clock                      |                 |         |           |       |      |  |  |  |

| Frequency of master clock         | MCLK            | 3.04    | 3.579     | 4.12  | MHz  |  |  |  |

| Duty ratio of master clock        |                 | 30      | 50        | 70    | %    |  |  |  |

| Filter                            |                 |         |           |       |      |  |  |  |

| Input sampling rate               |                 | _       | MCLK /4   | _     | MHz  |  |  |  |

| (DCLK=MCLK/K)                     |                 |         | WICER / I |       | WHIL |  |  |  |

| Output bit rate of digital filter | OWR             | -       | MCLK /128 | -     | MHz  |  |  |  |

| Corner frequency of high-pass     |                 | _       | 0.543     | _     | Hz   |  |  |  |

| filter (-3dB)                     |                 |         | 0.545     |       | 112  |  |  |  |

| Input/output                      |                 |         |           |       |      |  |  |  |

| High level output voltage lout    | V <sub>OH</sub> | VDD-0.5 | -         | -     | V    |  |  |  |

| = +5 mA                       |                 |    |     |     |    |  |

|-------------------------------|-----------------|----|-----|-----|----|--|

| Low level output voltage      | V               |    |     |     |    |  |

| Iout=-5mA                     | V <sub>OL</sub> | -  | -   | 0.5 | V  |  |

| Input leakage current         | I <sub>in</sub> | -  | ±10 | -   | μA |  |

| Capacitance of digital output | Cout            |    | 5   |     | nE |  |

| pin                           | COUT            | -  | 5   | _   | pF |  |

| UART                          |                 |    |     |     |    |  |

| 4800bps                       |                 | -2 |     | +2  | %  |  |

## 2. 5 Switching Characteristics

Pulse duty factor of CF output is 50%

本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。 This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format without prior permission of CHIPSEA

#### 3 **Application of the Chip**

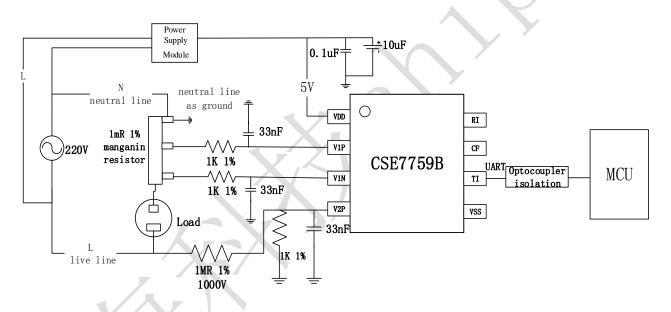

#### 3.1 Typical Application of CSE7759B

As shown in Figure 2, two small capacitors shall be connected in parallel on power supply terminal of CSE7759B to filter out high-frequency and low-frequency noise from power grid. The current signal is connected to CSE7759B after being sampled by manganin resistor and the voltage signal is inputted into CSE7759B after passing through resistor network. CSE7759B must be connected to the current signal and the voltage signal simultaneously but shall not be connected only to either signal.

Figure 2: Typical Application of CSE7759B (Isollation)

#### Note:

CSE7759B is a calibration-free electric energy measuring chip. The error of calibrated chip is ±2% upon delivery. Thus, final accuracy of external devices will influence overall accuracy of the products of the client. As for the device with accuracy of 1% indicated in Figure 2, the higher the accuracy is, the overall accuracy of the client will be.

As shown in Figure 2, it is the 1mR manganin resistor in current channel which influences current accuracy and it is 1M resistor and 1K resistor connected with it in voltage channel which influences voltage accuracy. When the accuracy of all three devices is within  $\pm 1\%$ , the overall

| 10/25                                 |                                                                                                                         |   |  |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|

| * * * * * * * * * * * * * * * * * * * | 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。                                                                                     |   |  |  |  |  |  |

| *                                     | This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format | - |  |  |  |  |  |

| *                                     | without prior permission of CHIPSEA                                                                                     |   |  |  |  |  |  |

error of CSE7759B without calibration may be controlled within  $\pm 3\%$ .

1M resistor in voltage channel shall select high pressure resistant 1000V 1% resistor (or with higher accuracy); otherwise, it is necessary to divide into five 0805 1% (or with higher accuracy) resistors. It is necessary to protect complete machine being damaged in the process of use due to insufficient withstanding voltage of resistor.

CSE7759B section collects strong current signal. As specified in safety regulation, the positions accessible to anybody shall be isolated. As shown in Figure 2, opto-isolator is used (the client may select isolation method of its own option and it is not limited).

Select neutral line or live line as ground. It is recommended to use neutral line as ground.

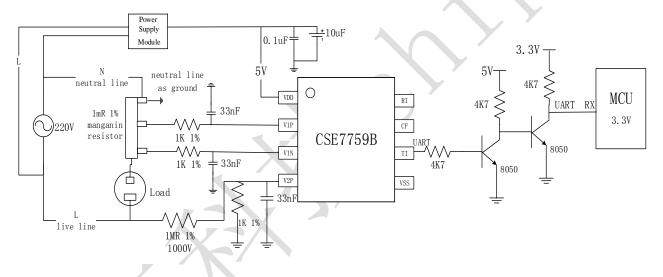

Figure 3: Typical Application of CSE7759B (Non-isollation)

Figure 3 shows CSE7759B non-isolation scheme. Operating voltage of MCU is 3.3V. If operating voltage of MCU is 5V, 200R resistor may be connected between TI and MCU.

#### 3. 2 Signal Frequency of Active Power $F_{CF}$

Internal DSP of CSE7759B has certain gain. Output frequency of active power may be calculated through the following formula after passing through frequency conversion module:

$$F_{CF} = \frac{V1 \times V2 \times 48}{V_{REF}^2} \times \frac{f_{osc}}{128}$$

V1: Voltage signal on current channel pin;

| 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                         |

| This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format |

| without prior permission of CHIPSEA                                                                                     |

V2: Voltage signal on voltage channel pin;

*f*<sub>osc</sub>: Built-in crystal oscillator; typical frequency is about 3.579MHz;

$V_{REF}$ : Built-in reference source; typical frequency is about 2.43V;

Note: There exists noise in CSE7759B. Therefore, for the purpose of ensuring the amplitude of properly measured effective values of current and voltage without signal input, current effective value applied on channel V1P\V1N shall not be lower than 40uv and voltage applied on channel V2P shall not be lower than 480uv. Please consult to technical support of the Company when using.

#### 3. 3 Measuring Range

Different manganin resistors (1mR manganin resistor is recommended) selected will influence current measuring range of CSE7759B directly.

The formula is as follows:

Full current measuring range(A) =  $\frac{43.75(\text{mV})}{\sqrt{2} * \text{manganin resistance} (\text{mR})}$

Such as: 1mR manganin resistor

Full current measuring range(A) =

$$\frac{43.75 \text{mV}}{\sqrt{2} * 1 \text{mR}} \approx 30.9 \text{A}$$

The current will reach  $\pm 2\%$  accuracy within the scope of 500:1; namely, the current will reach  $\pm 2\%$  accuracy within current measuring range of 1mR manganin resistor 30.9A~0.0618A; the accuracy will be larger than  $\pm 2\%$  when the current is smaller than 0.0618A.

If there is noise in PCB, such noise will influence the measuring accuracy. Thus, accuracy deviation caused by the noise in actual application should be taken into consideration as the influence of the noise on the signal is high (Consult to the Company before printing PCB).

The influence of PCB noise on the signal may be detected at the CF pin (pin7) of CSE7759B. Short-circuit at the manganin resistor. Observe when the current input signal is zero.

The larger manganin resistance is, the larger the signal frequency will be and the smaller the cycle will be.

Voltage accuracy is  $\pm 2\%$ .

Power measuring range will be determined by the current if the voltage is constant.

| ==/=>                                                                                                                   |                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                         | 1                                                                                                                                                              |

| 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。                                                                                     |                                                                                                                                                                |

| This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format |                                                                                                                                                                |

| without prior permission of CHIPSEA                                                                                     |                                                                                                                                                                |

|                                                                                                                         | 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。<br>This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format |

#### 3. 4 Serial Port Protocol

Relevant parameters of voltage, current, power and electric quantity could be read by the user through UART serial port protocol (RI and TI) and voltage, current, power and electric quantity could be obtained through calculation. At present, this serial port only supports baud rate of 4800bp (with allowable error of  $\pm 2\%$ ). Receive port RI is reserved temporarily and does not have actual function. The serial port will transmit data pockets of voltage coefficient, voltage cycle, current coefficient, current cycle, power coefficient, power cycle, calibration times and number of CF pulses through TI (transmit data in hexadecimal system).

Specific format of the data pocket is composed of: Packet header  $(2^{*}(1byte data+1bit even parity check)) \rightarrow voltage coefficient (3^{*}(1byte data +1bit even parity check)) \rightarrow voltage cycle (3^{*}(1byte data +1bit even parity check)) \rightarrow current coefficient (3^{*}(1byte data +1bit even parity check)) \rightarrow current cycle (3^{*}(1byte data +1bit even parity check)) \rightarrow power coefficient (3^{*}(1byte data +1bit even parity check)) \rightarrow power cycle (3^{*}(1byte data +1bit even parity check)) \rightarrow calibration times (1^{*}(1byte data +1bit even parity check)) \rightarrow number of CF pulses (2^{*}(1byte data +1bit even parity check)) \rightarrow Packet tail(1byte data +1bit even parity check).$

24byte totally; 54.912ms is used at 4800bps.

Byte No. data flow

Figure 4: Schematic Diagram of UART Data

|  | Tabl | e | 3- | 1 |

|--|------|---|----|---|

|--|------|---|----|---|

| Data Symbol         | High Byte | Medium Byte | Low Byte |

|---------------------|-----------|-------------|----------|

| Data Name           |           |             |          |

| Voltage coefficient | Ukh       | Ukm         | Ukl      |

| Voltage cycle       | Uth       | Utm         | Utl      |

| Current coefficient | Ikh       | Ikm         | Ikl      |

| 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------|

| This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format |

| without prior permission of CHIPSEA                                                                                     |

|                                                                                                                         |

| Current cycle       | Ith | Itm | Itl |  |

|---------------------|-----|-----|-----|--|

| Power coefficient   | Pkh | Pkm | Pkl |  |

| Power cycle         | Pth | Ptm | Ptl |  |

| Adj                 |     |     | Adj |  |

| Number of CF pulses |     | CFm | CFl |  |

The voltage coefficient, current coefficient and power coefficient are fixed values.

Specific data transmitted from the serial port is as follows:

| No. | Data Content    | Byte     | Not        | Calibrated | Abnormal |

|-----|-----------------|----------|------------|------------|----------|

|     |                 | Occupied | Calibrated |            |          |

| 1   | Packet header 1 | 1        | 0AAH       | 055H       | 0FxH     |

| 2   | Packet header 2 | 1        | 05AH       | 05AH       | 05AH     |

| 3   | Ukh             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 4   | Ukm             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 5   | Ukl             |          | 0FFH       | 0xxH       | 0xxH     |

| 6   | Uth             | 1        | 0xxH       | 0xxH       | 0xxH     |

| 7   | Utm             | 1        | 0xxH       | 0xxH       | 0xxH     |

| 8   | Utl             | 1        | 0xxH       | 0xxH       | 0xxH     |

| 9   | Ikh             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 10  | Ikm             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 11  | Ikl             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 12  | Ith             | 1        | 0xxH       | 0xxH       | 0xxH     |

| 13  | Itm             | 1        | 0xxH       | 0xxH       | 0xxH     |

| 14  | Itl             | 1        | 0xxH       | 0xxH       | 0xxH     |

| 15  | Pkh             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 16  | Pkm             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 17  | Pkl             | 1        | 0FFH       | 0xxH       | 0xxH     |

| 18  | Pth             | 1        | 0xxH       | 0xxH       | 0xxH     |

Table 3-2

| 14/25                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------|--|

| 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。                                                                                     |  |

| This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format |  |

| without prior permission of CHIPSEA                                                                                     |  |

|                                                                                                                         |  |

|    | checksum1   |   |      |      |      |  |

|----|-------------|---|------|------|------|--|

| 24 | Packet tail | 1 | 0xxH | 0xxH | 0xxH |  |

| 23 | CFl         | 1 | 0xxH | 0xxH | 0xxH |  |

| 22 | CFm         | 1 | 0xxH | 0xxH | 0xxH |  |

| 21 | Adj         | 1 | 0xxH | 0xxH | 0xxH |  |

| 20 | Ptl         | 1 | 0xxH | 0xxH | 0xxH |  |

| 19 | Ptm         | 1 | 0xxH | 0xxH | 0xxH |  |

x=0~F

(1) When packet header 1 is  $FxH(x=1 \sim F)$ , it indicates:

#### Table 3-3

| Packet header 1           | Description                                           |

|---------------------------|-------------------------------------------------------|

| Packet header 1.bit7~bit4 | =1111, fixed value.                                   |

| Packet header 1.bit3      | =1 indicates voltage cycle exceeds the range;         |

|                           | =0 indicates voltage cycle does not exceed the range; |

| Packet header 1.bit2      | =1 indicates current cycle exceeds the range;         |

|                           | =0 indicates current cycle does not exceed the range; |

| Packet header 1.bit1      | =1 indicates power cycle exceeds the range;           |

| 1                         | =0 indicates power cycle does not exceed the range;   |

| Packet header 1.bit0      | =1 indicates coefficient storage area (3n0h~3nFh) is  |

|                           | abnormal (n=A, B, C, D, E, F).                        |

| X.                        | =0 indicates coefficient storage area is normal.      |

Note: Maximum measurement is about 16s for current cycle, voltage cycle and active power cycle. It will prompt that the measuring range of corresponding cycle is exceeded after exceeded, as shown in Table 3-3.

The voltage or current signal cycle that is out of range, the 3byte signal is periodic and the corresponding values as invalid (voltage and current channel when there is no signal input, CSE7759B to about 2Hz voltage, current signal, so the detection of voltage and current when the cycle is out of range, generally abnormal situation, the chip itself damaged or external circuit problem).

The power cycle is out of range, and the voltage and current are out of range, the active power is 0, the current is about 0.

(2) Give prompt through packet header 1 whether the chip is calibrated according to the standard (0AAH indicates it has not been calibrated; 055H indicates it has been calibrated).(3) Checksum1 is the sum of all data except for packet header and packet tail lowering by 8bit and is used to verify whether the data received is correct after the data is received by the user.

(4) The unit for voltage cycle, current cycle and power cycle is us. When signal cycle is larger than 1s, the signal cycle will be outputted to the user immediately, and it will prompt through Adj.4(5 or 6) that it is an incomplete cycle. (For example, if signal cycle is 3.5s, 1s signal cycle will be outputted to the user when the accumulated cycle counts to 1s, and 1.5s signal cycle will be outputted to the user when the accumulated cycle counts to 1.5s instead the message is received by the user after reaching 3.5s so that the response speed is improved. When the signal amplitude to be measured declines, the signal cycle will increase.) (5)Adj:

| Adj    |                     | Des                 | cription               |                 |

|--------|---------------------|---------------------|------------------------|-----------------|

| Adj.0  | Calibration Addres  | s Selection 3n0H~:  | 3nFH(n=A,B,C,D,E,      | F)              |

|        | Adj.2               | Adj.1               | Adj.0                  | Remarks         |

| Adj.1  | 0                   | 0                   | 0                      | n=F             |

|        | 0                   | 0                   | 1                      | n=E             |

| A 11 Q | 0                   | 1                   | 0                      | n=D             |

| Adj.2  | 0                   | 1                   | 1                      | n=C             |

| X _    | 1                   | 0                   | 0                      | n=B             |

|        | 1                   | 0                   | 1                      | n=A             |

|        | 1                   | 1                   | 0                      | Calibration     |

|        |                     |                     |                        | disabled        |

| Adj.3  | Adj.3=1 indicates c | coefficient loading | error;                 |                 |

|        | Adj.3=0 indicates c | coefficient loading | is correct;            |                 |

| Adj.4  | Adj.4=1 indicates p | ower cycle of seria | al port outputted is a | complete cycle; |

Table 3-4

| 本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------|

| This document is exclusive property of CHIPSEA and shall not be reproduced or copied or transformed to any other format |

| without prior permission of CHIPSEA                                                                                     |

|       | Adj.4=0 indicates power cycle of serial port outputted is an incomplete cycle;   |

|-------|----------------------------------------------------------------------------------|

| Adj.5 | Adj.5=1 indicates current cycle of serial port outputted is a complete cycle;    |

|       | Adj.5=0 indicates current cycle of serial port outputted is an incomplete cycle; |

| Adj.6 | Adj.6=1 indicates voltage cycle of serial port outputted is a complete cycle;    |

|       | Adj.6=0 indicates voltage cycle of serial port outputted is an incomplete cycle; |

| Adj.7 | Number of pulses is overflowing; Simultaneous Adj.7 inversion                    |

- ♦ Adj0~2: is used to judge calibration data writing address when calibrating. For example Adj0~2=2, it indicates calibration address is 3D0H~3DFH in this time. The delivery calibration address is Adj0~2=0- namely, start from 3F0H~ 3FFH.

- Adj.3: Used to determine whether the coefficient load is correct.

- ◆ Adj.4: When power signal cycle is larger than 1s, present cycle counting time will be transmitted to the user. This flag bit is used to identify whether the power cycle outputted at this moment is complete power cycle or power cycle counting larger than 1s.

- ♦ Adj.5: When current signal cycle is larger than 1s, present cycle counting time will be transmitted to the user. This flag bit is used to identify whether the current cycle outputted at this moment is complete current cycle or current cycle counting larger than 1s.

- ♦ Adj.6: When voltage signal cycle is larger than 1s, present cycle counting time will be transmitted to the user. This flag bit is used to identify whether the voltage cycle outputted at this moment is complete voltage cycle or voltage cycle counting larger than 1s.

- ♦ Adj.7: Number of CF pulses will increase by 1 each time when one pulse signal is generated at CF pin (pin 7); when accumulated number of CF pulses is overflowing (overflowing when CFm: CFl=0FFFFH+1), negation will occurs to the value of calibration coefficient Adj.7 once.

## 3. 5 Chip Reset

After the chip reset, all the data is initialize, that is, the same as the initial power, waiting for about 550 ms, the serial port output signal starts to sample. How to judge the chip to generate the reset? When the current cycle value is 0, the initial power or reset of the chip is explained,

because the voltage and current are sampled in the chip, at least 800 ms time. Therefore, after the chip reset, at least 800 ms time current cycle is 0.

| f      |    |   | T          | rr |   |   |     |   |    | T  |          |   | [   |    | [      |    |   |   |        |    |    |            | /·····1 |

|--------|----|---|------------|----|---|---|-----|---|----|----|----------|---|-----|----|--------|----|---|---|--------|----|----|------------|---------|

| 55     | 5A | 2 | <b>C</b> 6 | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 45     | 51 | 0  | A4         | 36      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 48     | 51 | 1  | 58         | EE      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 46     | 51 | 2  | 0C         | A1      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 47     | 51 | 2  | <b>C</b> 0 | 56      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 49     | 51 | 3  | 73         | 0C      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 46     | 51 | 4  | 27         | BE      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 47     | 51 | 4  | DB         | 73      |

| 55     | 5A | 2 | <b>C</b> 6 | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 0 | 0   | 4B | 97     | 90 | 0 | 2 | 47     | 51 | 5  | 8F         | 28      |

| 55     | 5A | 2 | <b>C</b> 6 | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 46     | 71 | 6  | 43         | F4      |

| 55     | 5A | 2 | <b>C</b> 6 | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 49     | 71 | 6  | F7         | AB      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 48     | 71 | 7  | AA         | 5E      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 45     | 71 | 8  | 5F         | 11      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 48     | 71 | 9  | 12         | C8      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 47     | 71 | 9  | C6         | 7B      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 48     | 71 | 0A | 7A         | 31      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 83  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 48     | 71 | 0B | 2E         | E6      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 46     | 71 | 0B | E1         | 95      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 48     | 71 | 0C | 96         | 4D      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 46     | 71 | 0D | 49         | FF      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 47     | 71 | 0D | FD         | B4      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | OF | 0        | 1 | -F7 | 4B | 97     | 90 | 0 | 2 | 49     | 71 | 0E | B1         | 6B      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 46     | 71 | OF | 65         | 1D      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 47     | 71 | 10 | 19         | D3      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | 0F | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 47     | 71 | 10 | CD         | 87      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | 81  | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 46     | 71 | 11 | 80         | 3A      |

| 55     | 5A | 2 | C6         | FO | 0 | 2 | -81 | 0 | 3C | OF | 0        | 1 | F7  | 4B | 97     | 90 | 0 | 2 | 49     | 71 | 12 | 34         | F2      |

| •••••• |    |   | ••••••     |    |   |   |     |   |    |    | <b>T</b> |   | _   |    | •••••• |    |   |   | •••••• |    |    | ••••••     |         |

As shown in fig.5: current cycle is 8 times for 0.

Figure 5

#### 3.6 Calibration Mode

#### 3. 6. 1 Calibration Address Selection

After CSE7759B is powered on for the first time, calibration process shall be applied (when packet header 1: 0AAH, it indicates the chip shall be used after calibration. The chip will be calibrated once when being delivered): Read serial port data to obtain voltage cycle, current cycle and power cycle. Write the results into 3n0h~3nFh addresses (n=A, B, C, D, E, F) of the chip after calculation in upper computer in combination with calibration device. Details are as follows:

Table 3-5

| Address | Data Storage                                                 |

|---------|--------------------------------------------------------------|

| 3nFH    | (Calibration voltage cycle* calibration voltage) high 8bit   |

| 3nEH    | (Calibration voltage cycle* calibration voltage) medium 8bit |

| 3nDH    | (Calibration voltage cycle* calibration voltage) low 8bit    |

| 3nCH    | (Calibration current cycle* calibration current) high 8bit   |

| 3nBH    | (Calibration current cycle* calibration current) medium 8bit |

| 3nAH    | (Calibration current cycle* calibration current) low 8bit    |

| 3n9H    | (Calibration power cycle* calibration power) high 8bit       |

| 3n8H    | (Calibration power cycle* calibration power) medium 8bit     |

| 3n7H    | (Calibration power cycle* calibration power) low 8bit        |

| 3n6H    | Reserved                                                     |

| 3n5H    | Reserved                                                     |

| 3n4H    | Reserved                                                     |

| 3n3H    | Reserved                                                     |

| 3n2H    | Reserved                                                     |

| 3n1H    | Reserved                                                     |

| 3n0H    | Checksum2, 8bit                                              |

Note: Checksum2 = Sum of 3n7H~3nFH data; lowering by 8 bits.

◆Adj.bit2~bit0 (calibration times) calibration address selection:

#### Table 3-6

| 2 Bit | 1 Bit | 0 Bit | Remarks |

|-------|-------|-------|---------|

| 0     | 0     | 0     | n=F     |

| 0     | 0     | 1     | n=E     |

| 0     | 1     | 0     | n=D     |

| 0     | 1     | 1     | n=C     |

| 1     | 0     | 0     | n=B     |

| 1     | 0     | 1     | n=A     |

| 1 | 1 | 0 | Calibration |

|---|---|---|-------------|

|   |   |   | disabled    |

Allowable calibration times are 6 at present. The chip will be calibrated before it is delivered.

## 3. 6. 2 Delivery Calibration Parameters as Well as Current, Voltage and Power Formula of the Chip

Delivery calibration parameter of CSE7759B is 1mR manganin resistor (resistor at V1P and V1N will be identified as V1R hereunder) at V1P and V1N, and is 1M resistor at V2P (resistor at V2P will be identified as V2R hereunder) and input load signal is 5A, 220V(see Figure 2). Thus, V1R and V2R may be neglected when calculating if external hardware is consistent with calibration parameter upon delivery.

◆Current calculation formula:

Measured current

$$Ix(A) = \frac{current coefficient (hexadecimal number)}{current cycle (hexadecimal number) * V1R}$$

◆ Voltage calculation formula:

Measured voltage Ux(V) =

$$\frac{\text{voltage coefficient (hexadecimal number) } * V2R}{\text{voltage cycle (hexadecimal number)}}$$

◆ Power calculation formula:

Measured power  $Px(W) = \frac{Power coefficient (hexadecimal number) * V2R}{Power cycle (hexadecimal number) * V1R}$

Note: If the parameter at V1P and V1N is 1mR manganin resistor, V1R=1; if the parameter at V1P and V1N is 2mR manganin resistor, V1R=2 and so forth; if the parameter at V2P is 1M resistor, V2R=1; if the parameter at V2P is 2M resistor, V2R=2 and so forth.

It is only the chip that is calibrated upon delivery calibration rather than complete machine. Thus, little error will exist (different from the noise generated by PCB; the error range is different tool). If the error is unacceptable to the user after testing, it may be calibrated by the user. Consult to the Company for details.

## 3. 7 Electric Quantity Calculation

## 3.7.1 Frequency of CF

20/25

Internal DSP of CSE7759B has certain gain. Output frequency of active power may be calculated through the following formula after passing through frequency conversion module:

$$F_{CF} = \frac{V1 \times V2 \times 48}{V_{REF}^2} \times \frac{f_{osc}}{128}$$

V1: Voltage signal on current channel pin;

V2: Voltage signal on voltage channel pin;

$f_{osc}$ : Built-in crystal oscillator; typical frequency is about 3.579MHz;

$V_{REF}$ : Built-in reference source; typical frequency is about 2.43V;

Note: There exists noise in CSE7759B. Therefore, for the purpose of ensuring the amplitude of properly measured effective values of current and voltage without signal input, current effective value applied on channel V1P\V1N shall not be lower than 40uv and voltage applied on channel V2P shall not be lower than 480uv. Please consult to technical support of the Company when using.

For example: If the current is 5A, it will be a 1mR manganin resistor; if the voltage is 200V, it will be a 1k divider resistor (Refer to circuit of Figure 2).

$$F_{CF} = \frac{1mR \times 5A \times 200V \times 1K/1M \times 48}{2.43V^2} \times \frac{3.579MHz}{128} \approx 227\text{Hz} \quad \text{(Theoretical value)}$$

## 3. 7. 2 Current Example of Electric Quantity Calculation

The serial port outputs overflow flags of 2byte number of pulses and 1bit number of pulses (Adj.bit7). Value negation will occur to Adj.bit7 once when number of pulses is overflowing. The user could calculate current electric quantity by accumulating number of pulses.

Note: Overflowing times of number of pulses =n; number of 2byte pulses =y

Current Electric Quantity Theoretical Value(kW.h) =

$$\frac{\text{Total number of pulses}}{\text{Number of pulses a kilowatt hour}}$$

=  $\frac{n \times 65536 + y}{227Hz \times 3600s}$

As for fixed hardware (manganin), one kilowatt hour generates fixed pulses. Thus, number of pulses generated by kilowatt hour is a fixed value.

According to power coefficient= Calibration power cycle\* Calibration power, power frequency of at 1000W is:

$$F_{CF}'(Hz) = \frac{V1R * 10^9}{\text{Power coefficient} * V2R}$$

(Note: Refer to 3.5.2 for valuing of V1R and V2R)

Then, actual value of electric quantity at present is:

Current power (kW. h) =  $\frac{\text{total number of pulses}}{\text{Number of pulses a kilowatt hour}} = \frac{n \times 65536 + y}{F_{CF}' \times 3600s}$

It is one kilowatt hour when 1000W load operates by one hour.  $F_{CF}' \times 3600$ s in the above example is the number of pulses after 1000W load operates by one hour. It means the number of pulses generated by one kilowatt hour. Operating time of the load will change if the load varies when the number of pulses in one kilowatt hour remains unchanged.

As for different hardware, theoretical value of number of pulses in one kilowatt hour deviates from the actual value. If higher measuring accuracy is required, actual  $F_{CF}$  must be used for calculation.

#### 3.8 voltage, current, active power calculation reference flow chart

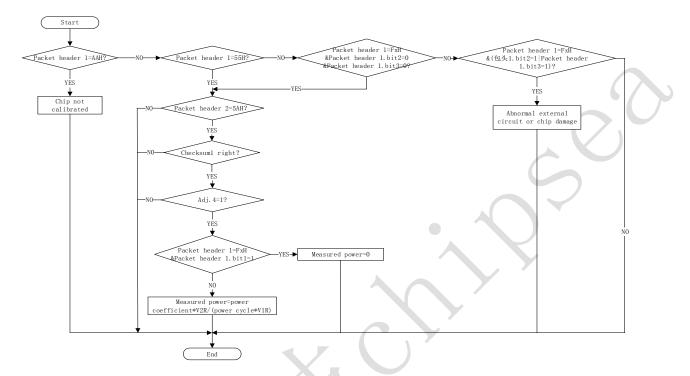

In order to represent the voltage, current and active power flow, a typical application flow chart is introduced.

#### 3.8.1 voltage operation reference flow chart

Figure 6: voltage operation flow chart

## 3.8.2 current operation reference flow chart

| 2 | 3/ | 2 | 5 |

|---|----|---|---|

#### 3. 8. 3 Active power operation reference flow chart

Figure 8: active power flow charts

#### 3. 9 Boot Threshold and Shunt Running Prevention of the Chip

CSE7759B adopts new-type shunt running prevention algorithm. Only if power value of input signal is larger than internal noise value, will the measuring module will start measuring normally.

#### 3. 10 Built-in Oscillator

Frequency of built-in oscillator used on CSE7759B is about 3.579M. Power supply rejection ratio is <0.01/V.

#### 3.11 Built-in Reference Source

CSE7759B is fitted with built-in high-accuracy bandgap reference source. Typical voltage outputted by reference source is 2.43V.

聚点滴之芯·成浩瀚之海

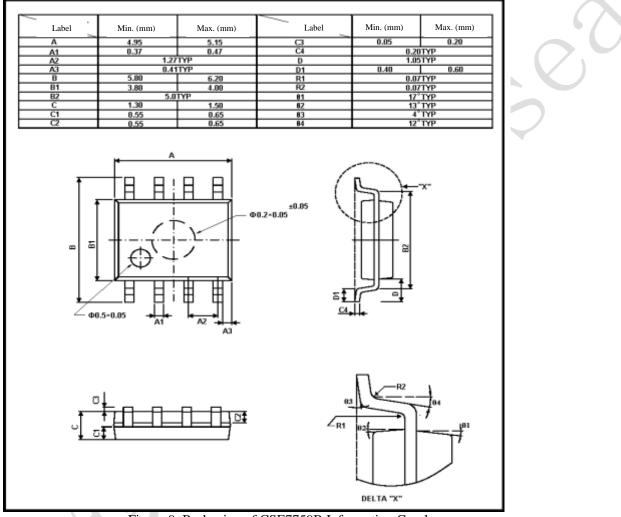

## 4 Packaging of CSE7759B

CSE7759B is packaged in SOP8. Refer to the following figure for specific packaging information:

Figure 9: Packaging of CSE7759B Information Graph

25/25