Shared RAM CPU FPGA¶

La commande (monitor) pour ecrire dans la DDR monitor¶

Usage:

read addr: address

write addr: address value

read analog mixed signals: -ams

set slow DAC: -sdac AO0 AO1 AO2 AO3 [V]

code source

https://github.com/RedPitaya/RedPitaya/tree/master/Test/monitor

Cache¶

https://docs.xilinx.com/r/en-US/oslib_rm/Arm-Cortex-A53-64-bit-Processor-Cache-Functions

https://github.com/Xilinx/embeddedsw/blob/master/lib/bsp/standalone/src/arm/cortexa9/xil_cache.h

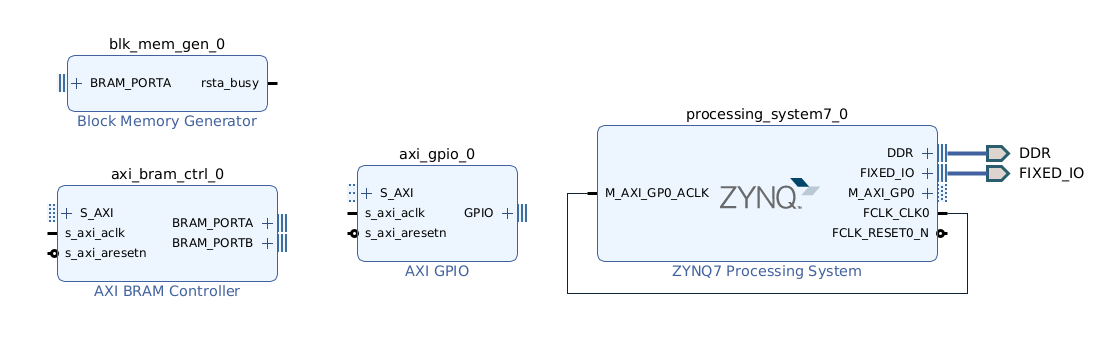

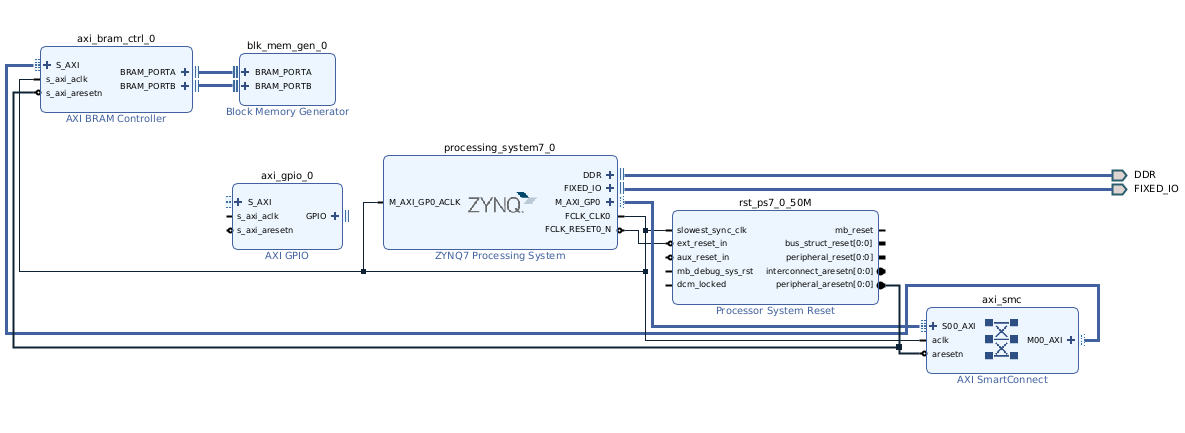

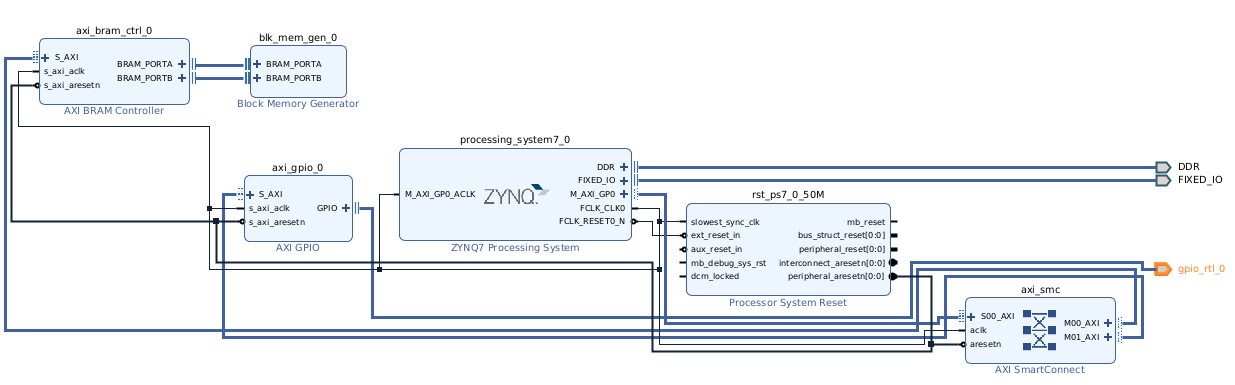

Create Block¶

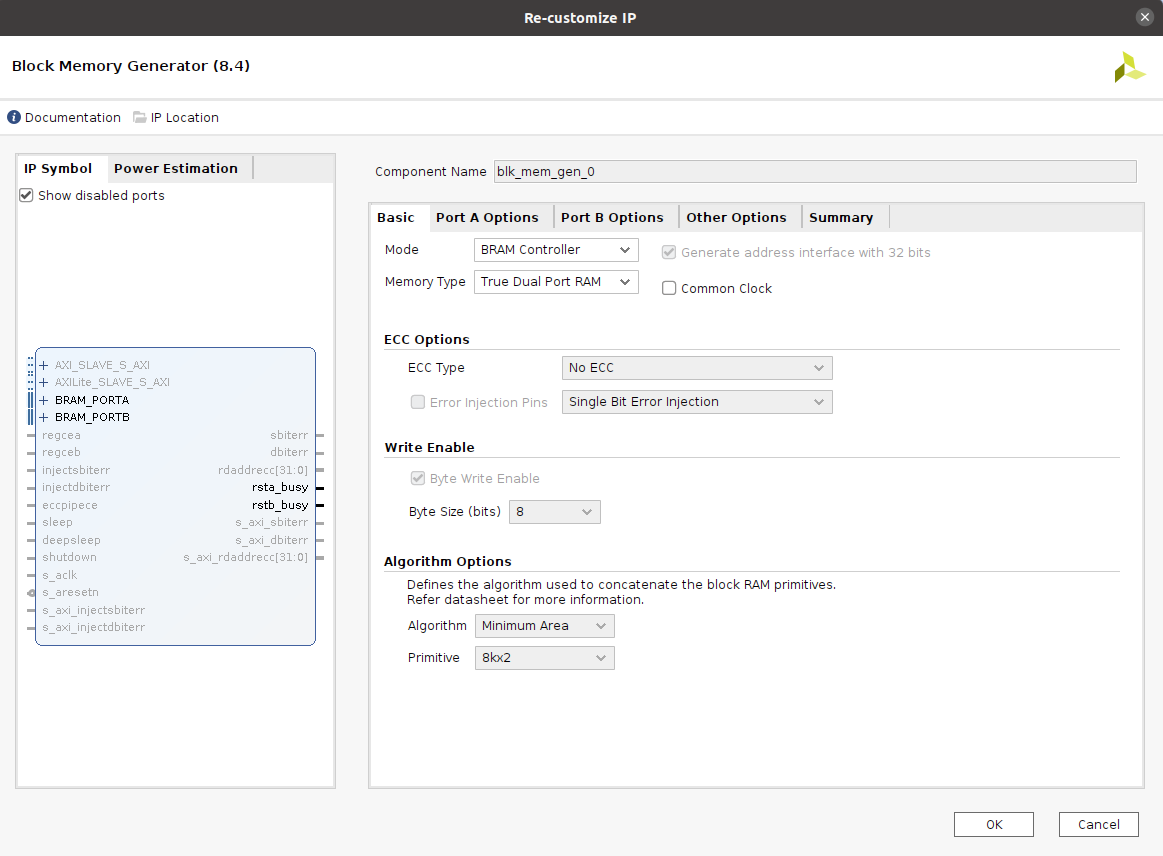

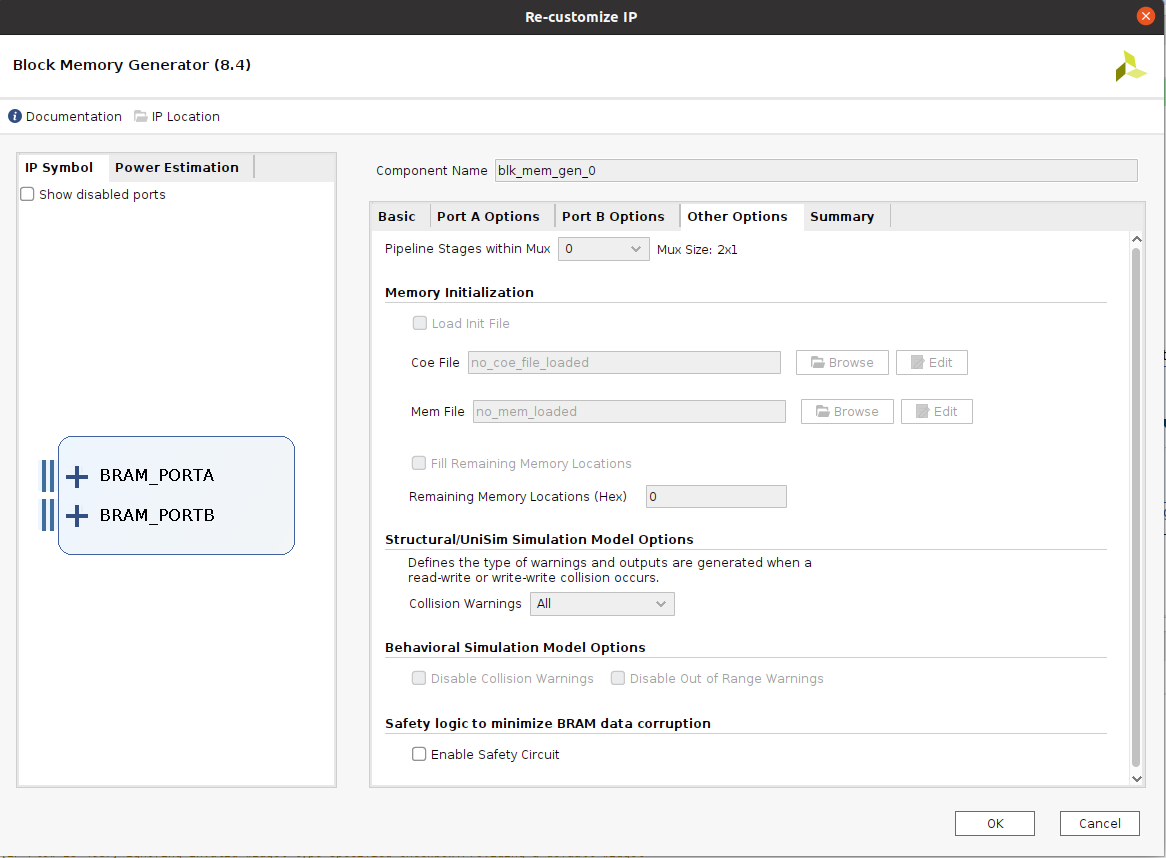

Configure BRAM

Memory Type: True Dual Port RAM

(Disable) Enable Safety Circuit

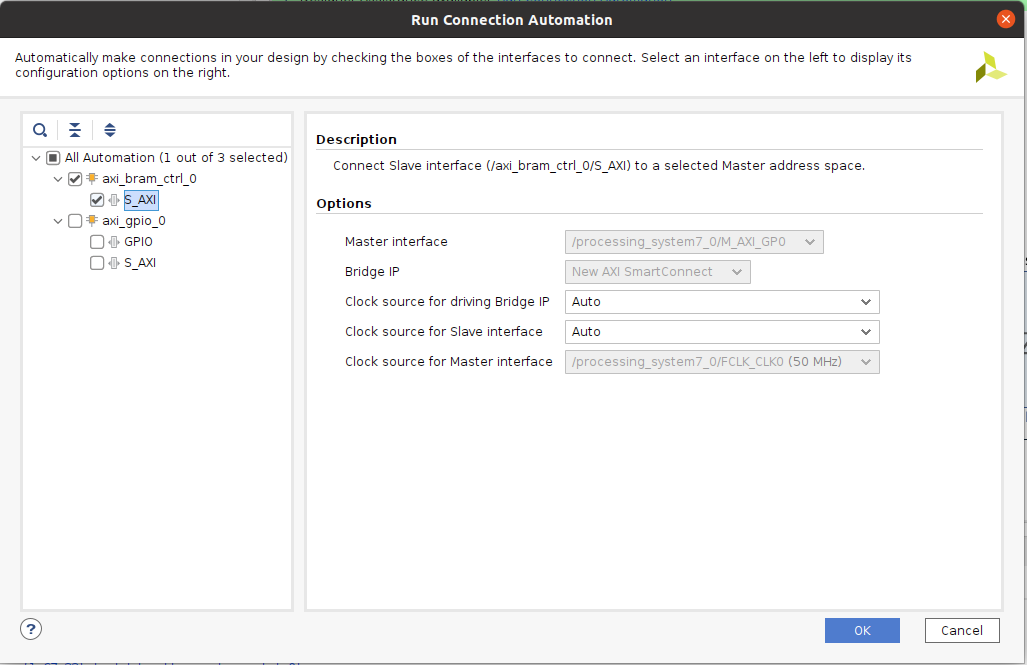

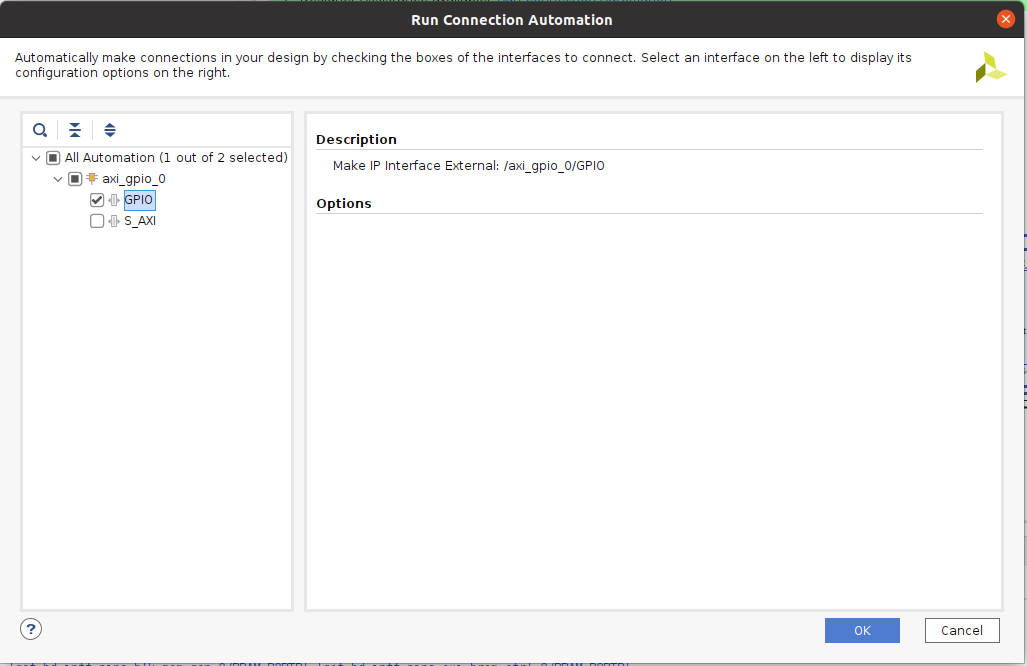

Run Connection Automation axi_gpio_0/S_AXI

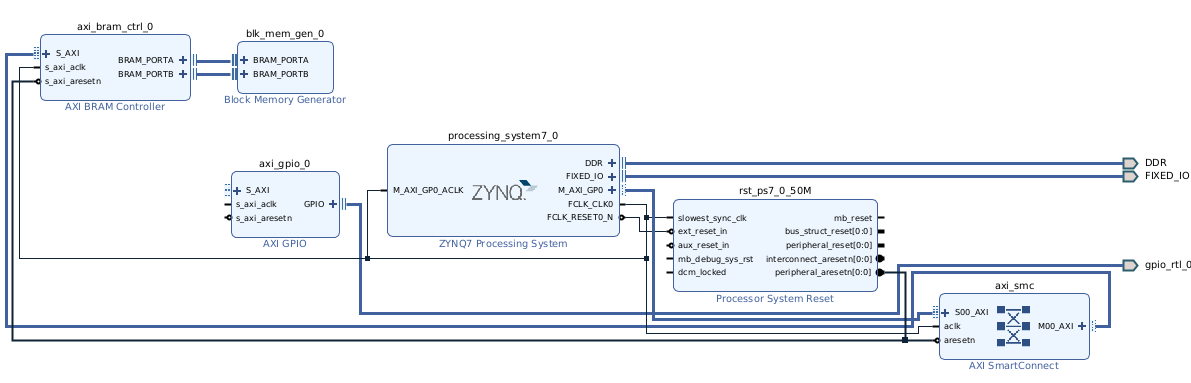

after Automation¶

Run Connection Automation axi_gpio_0/gpio

After Automation

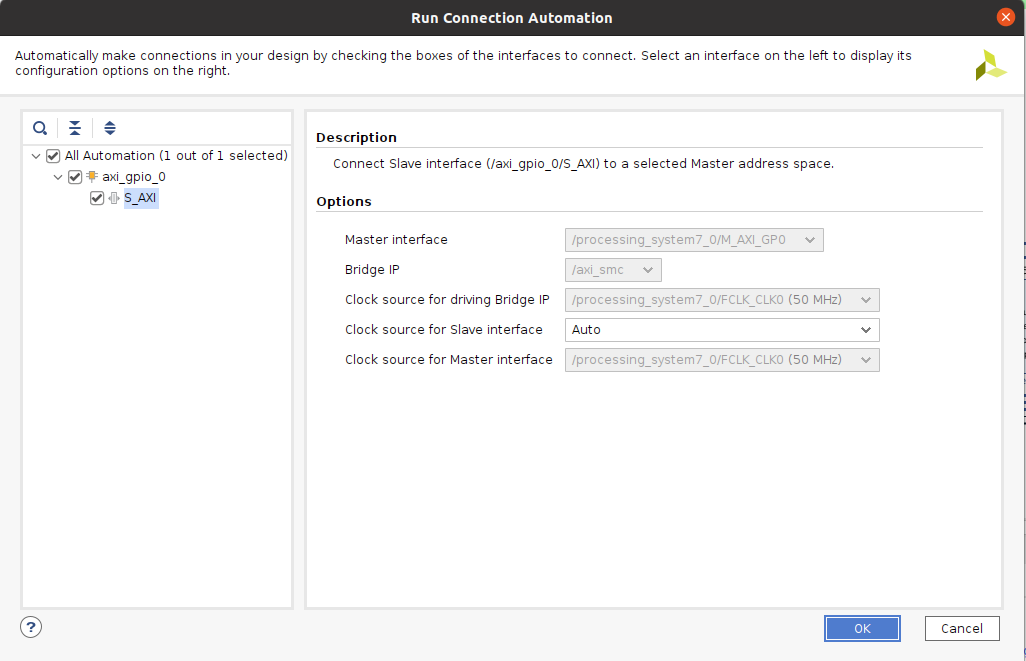

Run Connection Automation axi_gpio_0/gpio

After Automation

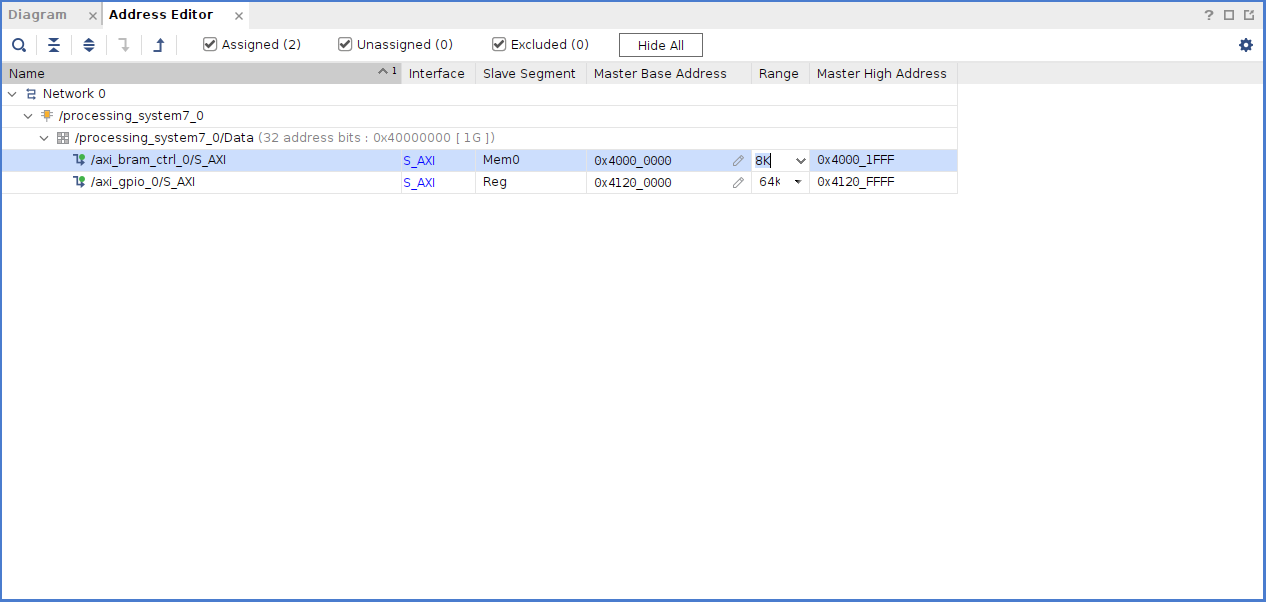

Address Editor

Ecriture dans la RAM¶

Utilisation du programme :

memrw.c

Source:¶

https://www.geii.eu/index.php?option=com_content&view=article&id=236&Itemid=933#introduction

https://support.xilinx.com/s/question/0D52E00006hplPeSAI/axi4-stream-fifo-keeps-data?language=en_US

https://forum.digilent.com/topic/3822-what-is-the-fastest-way-to-save-pl-data/

https://lniv.fe.uni-lj.si/redpitaya/redpitaya-classic.htm

https://docs.xilinx.com/r/en-US/ug1399-vitis-hls/Automatic-Port-Width-Resizing

Updated by Frédéric Blanc about 1 year ago · 15 revisions