Actions

DLPC410 » History » Revision 6

« Previous |

Revision 6/13

(diff)

| Next »

Frédéric Blanc, 2017-04-27 14:33

DLPC410¶

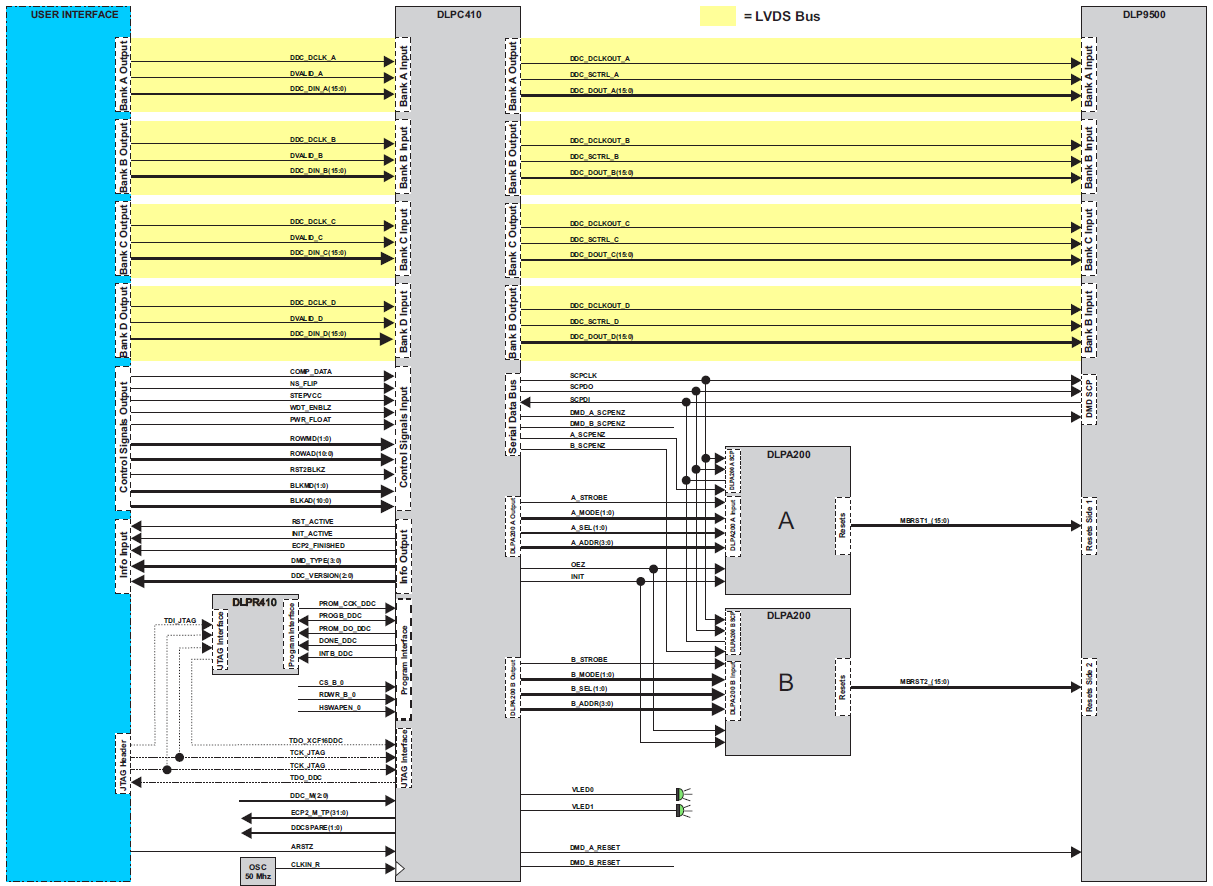

| BLOCK | NAME | BUS | TYPE | DLPC I/O | DESCRIPTION |

|---|---|---|---|---|---|

| A | DDC_DIN_A | 16 | LVDS | I | Data A bus Input |

| DVALID_A | LVDS | I | Bank A Valid Input Signal | ||

| DDC_DCLK_A | LVDS | I | Bank A Input Clock | ||

| B | DDC_DIN_B | 16 | LVDS | I | Data B bus Input |

| DVALID_B | LVDS | I | Bank B Valid Input Signal | ||

| DDC_DCLK_B | LVDS | I | Bank B Input Clock | ||

| C | DDC_DIN_C | 16 | LVDS | I | Data C bus Input |

| DVALID_C | LVDS | I | Bank C Valid Input Signal | ||

| DDC_DCLK_C | LVDS | I | Bank C Input Clock | ||

| D | DDC_DIN_D | 16 | LVDS | I | Data D bus Input |

| DVALID_D | LVDS | I | Bank D Valid Input Signal | ||

| DDC_DCLK_D | LVDS | I | Bank D Input Clock | ||

| Ctrl_Sig_In | COMP_DATA | SE | I | Compliment Data (0 <--> 1) | |

| NS_FLIP | SE | I | Top/Bottom image flip on DMD | ||

| STEPVCC | SE=.I | Not Used | |||

| WDT_ENBLZ | SE=.I | DMD Mirror Clocking PulseWatchdog Timer Enable | |||

| PWR_FLOAT | SE=.I | DMD Power Good indicator | |||

| ROWMD | 2 | SE=.I | DMD Row Mode | ||

| ROWAD | 11 | SE=.I | DMD Row Address | ||

| RST2BLK | SE=.I | Dual Block Reset bit | |||

| BLKMD | 2 | SE=.I | Block Mode | ||

| BLKAD | 11 | SE=.I | Block Address | ||

| Info Out | RST_ACTIVE | O | SE | DMD Reset in Progress | |

| INIT_ACTIVE | O | SE | DLPC410 Initilization Routine Active | ||

| ECP2_FINISHED | O | SE | DLPR410 Initialization Routine Complete | ||

| DMD_TYPE | 4 | O | SE | DMD Attached Type | |

| DDC_VERSION | 3 | O | SE | DLPC410 Firmware Rev Number |

Updated by Frédéric Blanc almost 8 years ago · 13 revisions